东京工业大学的科学家报告称,两种创新设计技术可显着提高分数 N 锁相环 (PLL) 的性能。所提出的方法旨在最大限度地减少称为分数杂散的

东京工业大学的科学家报告称,两种创新设计技术可显着提高分数 N 锁相环 (PLL) 的性能。所提出的方法旨在最大限度地减少称为分数杂散的不需要的信号,这种信号通常困扰许多现代雷达系统和无线收发器中使用的 PLL。这些努力可以为 5G 时代之后无线通信、自动驾驶汽车、监控和跟踪系统的技术改进打开大门。

许多新兴和不断发展的技术,例如自动驾驶车辆、目标跟踪系统和远程传感器,都依赖于无线数据收发器和雷达系统的高速、无差错运行。在这些应用中,锁相环 (PLL) 是帮助振荡信号合成、调制和同步的关键组件。因此,消除或最小化 PLL 中的误差源对于提高系统的整体性能至关重要。

在分数 N PLL 中,一种流行的 PLL 类型具有出色的分辨率和对频率、抖动和分数杂散的灵活控制,是主要的敌人。“抖动”是指与合成振荡的理想时序的总体偏差。另一方面,分数杂散是由于误差的周期性而产生的不需要的信号。数字 PLL 中通常使用称为数字时间转换器 (DTC) 的组件来消除量化误差,但由于所谓的“积分非线性 (INL)”而导致的 DTC 缺陷最终表现为导致相位劣化的分数杂散PLL 输出中的噪声。

在最近的一项研究中,由冈田健一 (Kenichi Okada) 教授领导的东京工业大学 (Tokyo Tech) 的一个研究小组试图通过开发两种创新设计技术来解决这些问题,从而形成低杂散分数 N PLL。他们的工作已发表在2024 年 IEEE 国际固态电路会议(ISSCC)的会议记录上。

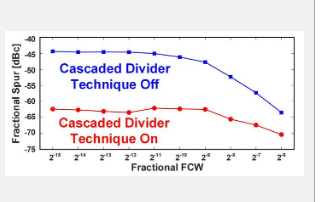

第一个提出的技术涉及使用级联小数分频器。此方法涉及将频率控制字 (FCW)(控制输出频率的内部 PLL 信号)分成两部分,但两者都远离整数值。其背后的逻辑是,对于远整数 FCW,分数杂散会以较高频率出现在 PLL 中,并且高频分量自然会被 PLL 的固有操作滤除(图 1)。值得注意的是,这种方法不涉及数字预失真(DPD),这种技术会带来复杂性并导致锁相速度变慢。

提出的第二种技术围绕伪差分 DTC 来避免标准 DTC 实施的陷阱(图 2)。“在传统的 DTC 设计中,DTC 功率、延迟范围、噪声和 INL 之间存在严格的权衡,限制了可实现的最小分数杂散水平,”Okada 教授解释道。为了解决这个问题,研究人员指出,DTC 的非线性甚至包含对称分量。因此,他们在差分操作中使用两个具有相同偶对称 INL 的半范围 DTC 来实现单个 DTC 的功能。因此,这些 INL 自然会通过 PLL 相位检测器的减法被抵消。

该团队通过使用 65 nm CMOS 工艺实现所提出的数字 PLL 来测试他们的想法,仅需要 0.23 mm 2的有源电路面积。通过将其设备的性能与其他最先进的设计进行比较,研究人员注意到了几个优点。“通过抑制分数杂散,集成 PLL 抖动从 243.5 fs 降低到 143.7 fs,”Okada 教授强调道。“得益于所提出的级联小数分频器和伪差分 DTC 技术,我们无需 DPD 技术即可实现最低级别的抖动。”

运气好的话,这种创新设计将带来许多以分数 N PLL 为支柱的应用的技术改进。

这些研究成果部分来自日本国立信息通信技术研究所(NICT)的委托研究(No. JPJ012368C00801)。

声明本站所有作品图文均由用户自行上传分享,仅供网友学习交流。若您的权利被侵害,请联系我们